Your What is behavioural modelling in verilog images are ready in this website. What is behavioural modelling in verilog are a topic that is being searched for and liked by netizens now. You can Get the What is behavioural modelling in verilog files here. Get all free images.

If you’re searching for what is behavioural modelling in verilog images information connected with to the what is behavioural modelling in verilog topic, you have pay a visit to the right blog. Our website frequently provides you with hints for seeing the maximum quality video and picture content, please kindly hunt and locate more informative video articles and images that fit your interests.

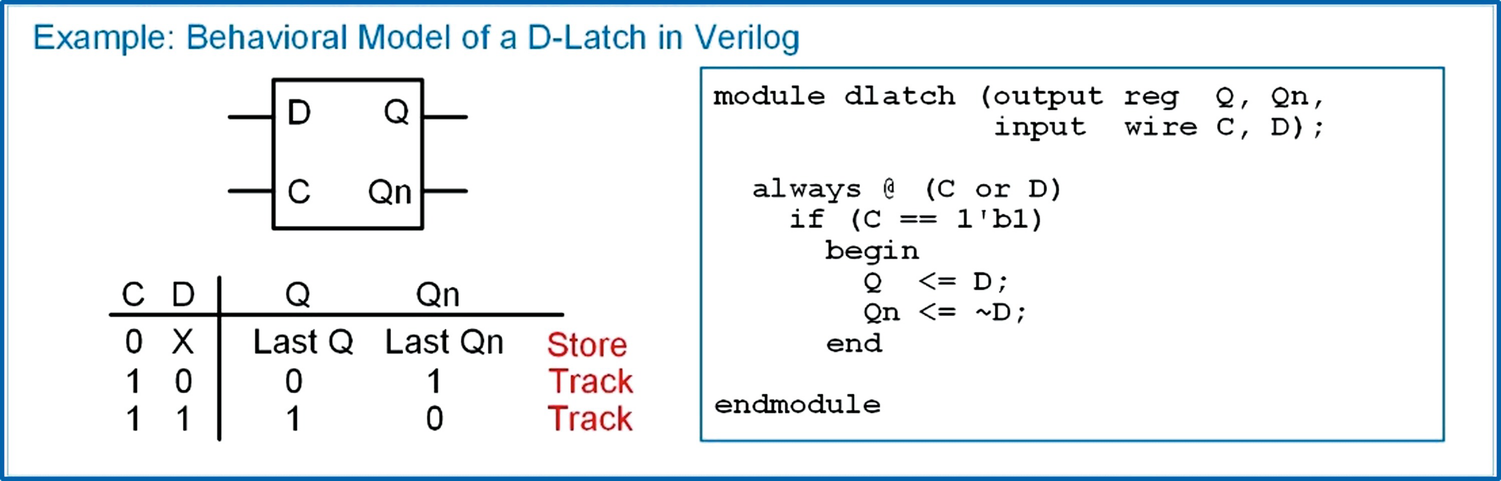

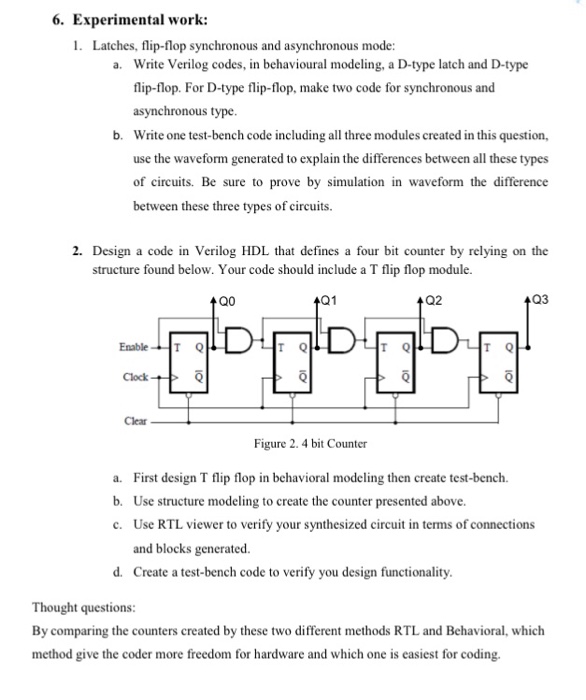

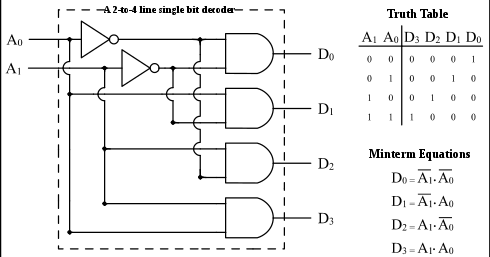

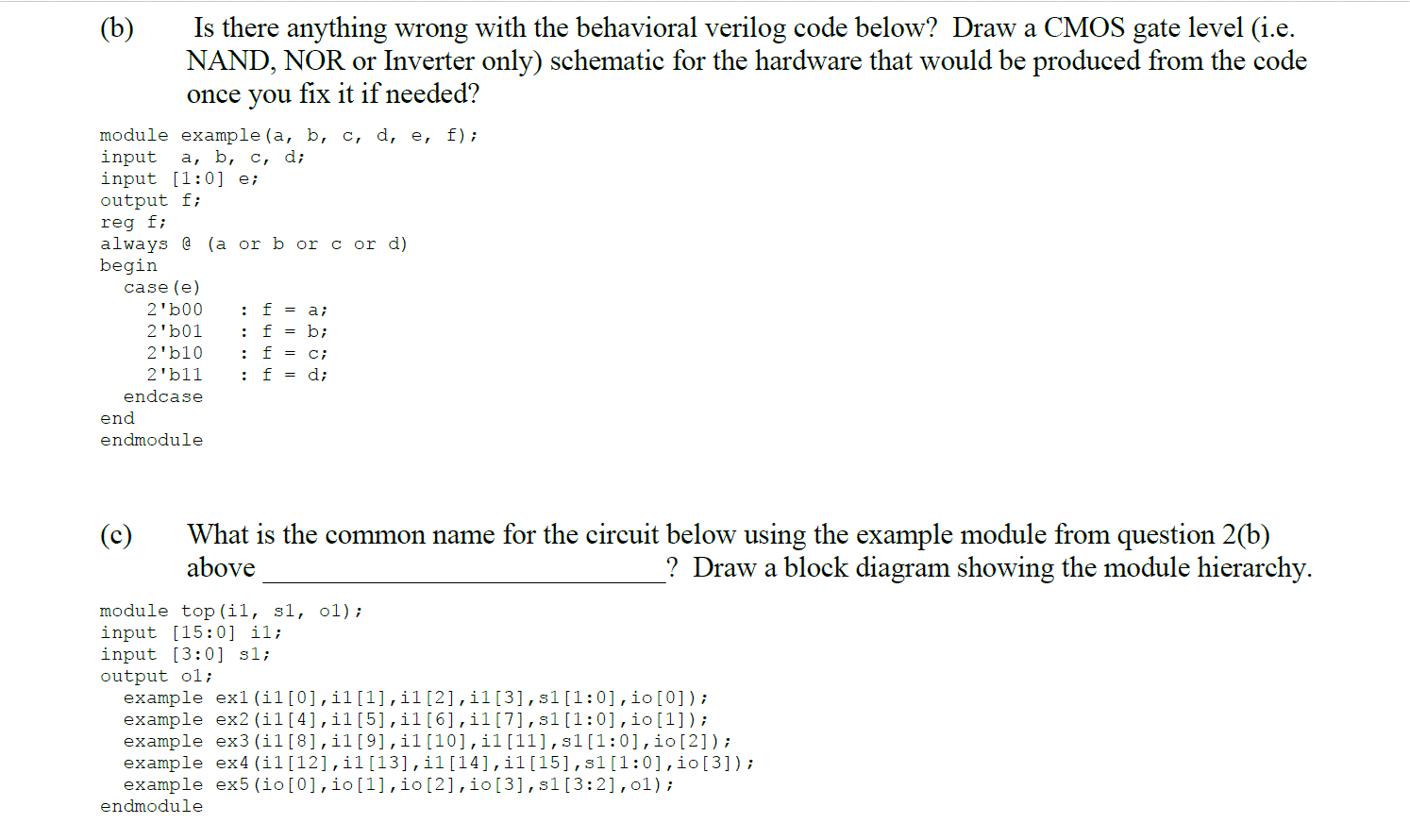

What Is Behavioural Modelling In Verilog. Each of the technique has an action flow related with it. The behavioral modeling describes how the circuit should behave. The initial statements are executed once and the always statements are executed repetitively. On the other hand The Behavioral modeling in Verilog is used to describe the function of a design in an algorithmic manner so if i want to describe a 2 to 4 decoder in dataflow modeling i would be like this.

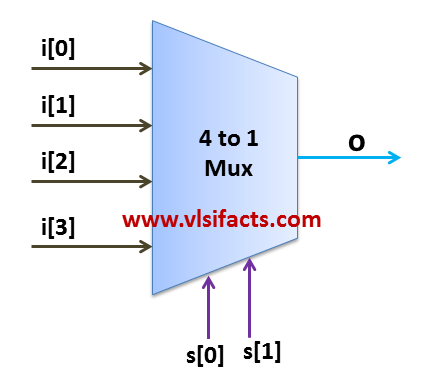

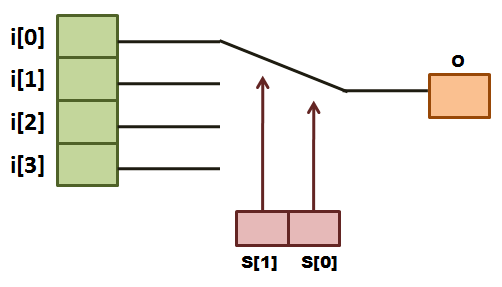

Different Coding Styles Of Verilog Language Vlsifacts From vlsifacts.com

Different Coding Styles Of Verilog Language Vlsifacts From vlsifacts.com

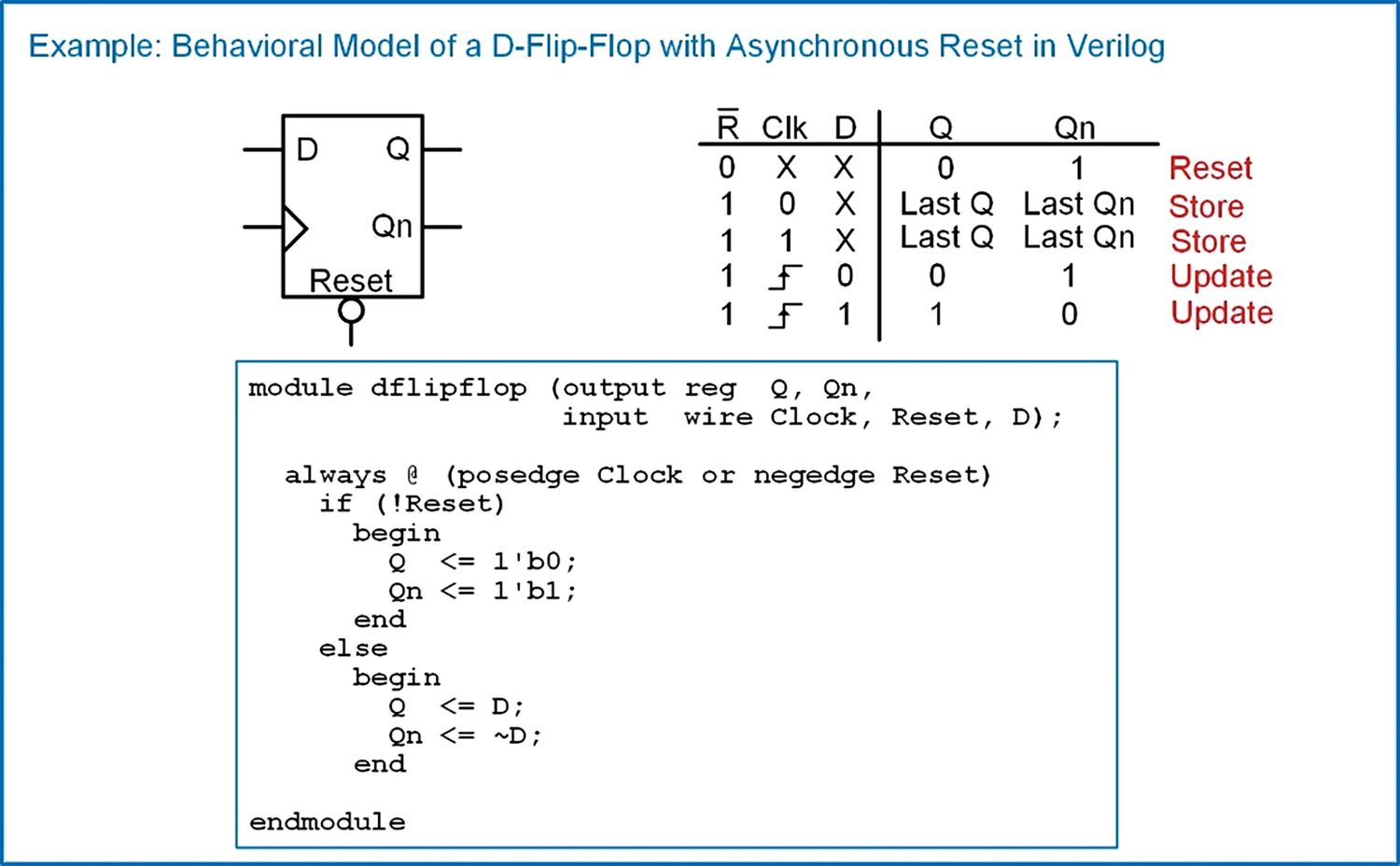

Verilog supports design that can be represented in different modeling levels. The VHDL synthesizer tool decides the actual circuit implementation. The behavioral model describes a system in an algorithmic way. Read more elaboration about it is given here. It is used mostly to describe sequential circuits but can be used to describe combinational circuits. EE577b Verilog for Behavioral Modeling Nestoras Tzartzanis 10 February 3 1998 Data Types.

Behavioral modeling is used to describe complex circuits.

Behavioral modeling attempts to explain why an individual makes a decisions and the model is then used to help predict future behavior. It is commonly used to describe consecutive circuits but can also be used to define aggregate circuits. The behavioral model describes a system in an algorithmic way. EE577b Verilog for Behavioral Modeling Nestoras Tzartzanis 10 February 3 1998 Data Types. VHDL Behavioral Modeling Style. As a designer we just need to know the algorithm behavior of how we want the system to work.

Source: link.springer.com

Source: link.springer.com

A dataflow architecture uses only concurrent signal assignment statements. This is a very powerful abstraction technique. This page contains Verilog tutorial Verilog Syntax Verilog Quick Reference PLI modelling memory and FSM Writing Testbenches in Verilog Lot of Verilog Examples and Verilog in One Day Tutorial. Behavioral modeling represents digital circuits at an active and prepared level. For these reasons behavioral modeling is considered highest abstraction level as compared to data-flow or structural models.

Furthermore the behavioral model helps in controlling the simulation and manipulate variables of the data types. The VHDL synthesizer tool decides the actual circuit implementation. In Verilog HDL transistors are known as Switches that can either conduct or open. Each of the procedure has an activity flow associated with it. These all statements are contained within the procedures.

Source: technobyte.org

Source: technobyte.org

Behavioral modeling is the highest level of abstraction in the Verilog HDL. Here each algorithm is sequential. These all statements are contained within the procedures. The behavioral modeling describes how the circuit should behave. In Verilog HDL transistors are known as Switches that can either conduct or open.

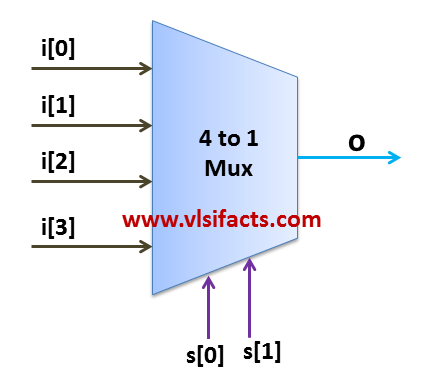

Source: vlsifacts.com

Source: vlsifacts.com

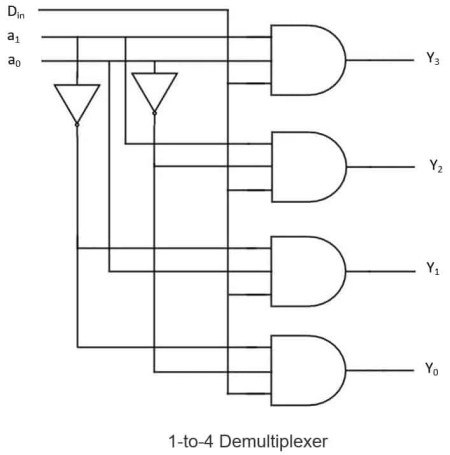

Module decoder2to4 e i d. Companies use behavioral modeling to target. The VHDL synthesizer tool decides the actual circuit implementation. On the other hand The Behavioral modeling in Verilog is used to describe the function of a design in an algorithmic manner so if i want to describe a 2 to 4 decoder in dataflow modeling i would be like this. In other words each algorithm consists of a set of instructions that execute one after the other.

Source: link.springer.com

Source: link.springer.com

Behavioral models in Verilog contain procedural statements which control the simulation and manipulate variables of the data types. The behavioral modeling describes how the circuit should behave. Furthermore the behavioral model helps in controlling the simulation and manipulate variables of the data types. Behavioral modeling represents digital circuits at an active and prepared level. Behavioral modeling attempts to explain why an individual makes a decisions and the model is then used to help predict future behavior.

Source: vlsifacts.com

Source: vlsifacts.com

The abstraction in this modeling is as simple as writing the logic in C language. The difference between these styles is based on the type of concurrent statements used. Companies use behavioral modeling to target. Behavioral modeling represents digital circuits at an active and prepared level. Behavioral modeling is used to describe complex circuits.

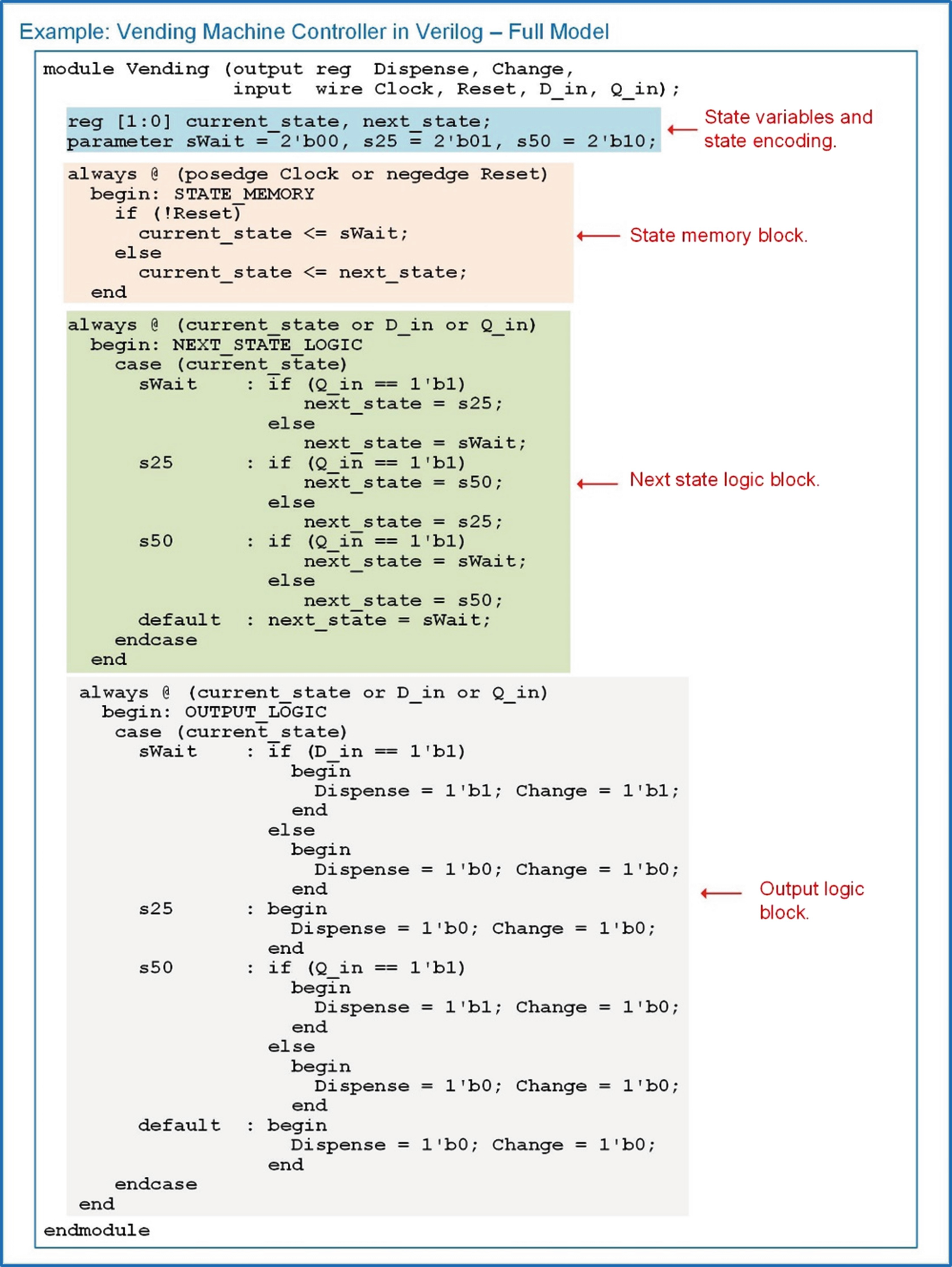

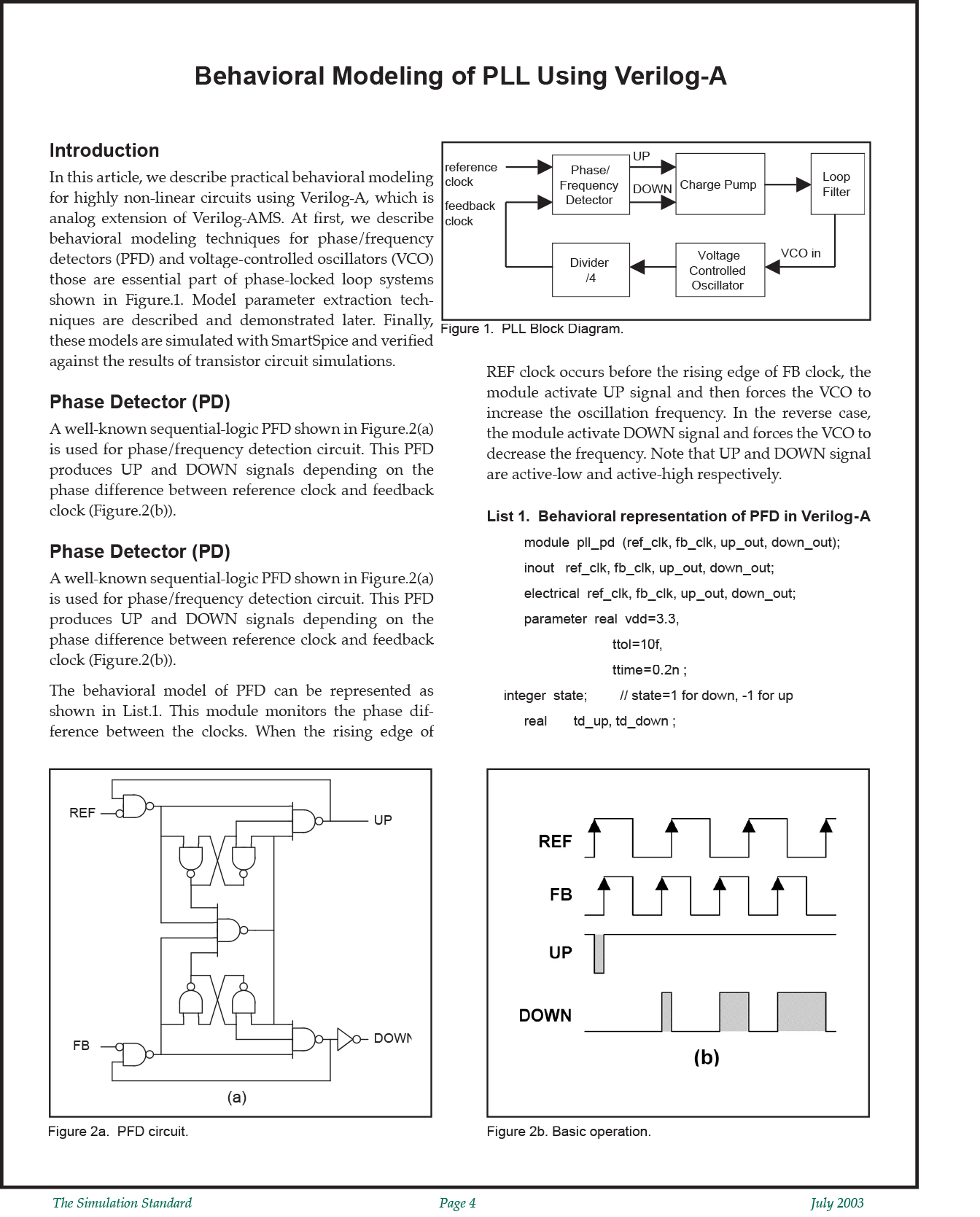

Source: silvaco.com

Source: silvaco.com

On the other hand The Behavioral modeling in Verilog is used to describe the function of a design in an algorithmic manner so if i want to describe a 2 to 4 decoder in dataflow modeling i would be like this. Verilog supports design that can be represented in different modeling levels. The abstraction in this modeling is as simple as writing the logic in C language. Unlike gate and dataflow modeling behavior modeling does not demand knowing logic circuits or logic equations. It is used mostly to describe sequential circuits but can be used to describe combinational circuits.

Source: slideplayer.com

Source: slideplayer.com

Furthermore the behavioral model helps in controlling the simulation and manipulate variables of the data types. Furthermore the behavioral model helps in controlling the simulation and manipulate variables of the data types. Module decoder2to4 e i d. It is commonly used to describe consecutive circuits but can also be used to define aggregate circuits. The abstraction in this modeling is as simple as writing the logic in C language.

Source: youtube.com

Source: youtube.com

Behavioral modeling represents digital circuits at an active and prepared level. These all statements are limited within the processes. This is a very powerful abstraction technique. Here the behavioral modeling concept will be. Feb-9-2014 Sequential Statement Groups.

Source: youtube.com

Source: youtube.com

Unlike gate and dataflow modeling behavior modeling does not demand knowing logic circuits or logic equations. VHDL Behavioral Modeling Style. Module decoder2to4 e i d. Here each algorithm is sequential. This is a very powerful abstraction technique.

Source: docsity.com

Source: docsity.com

They require some knowledge of how hardware or hardware signals work. The abstraction in this modeling is as simple as writing the logic in C language. It is primarily used to model sequential circuits but can also be used to model pure combinatorial circuits. The other modeling techniques are relatively detailed. Behavioral models in Verilog contain procedural statements which control the simulation and manipulate variables of the data types.

Source: learnpick.in

Source: learnpick.in

The concept of marketing ethics in the integration circuits will be introduced here. What is Behavioral Model in Verilog. Behavioral models in Verilog comprise practical statements which control the replication and operate variables of the data types. It is primarily used to model sequential circuits but can also be used to model pure combinatorial circuits. Behavioral modeling is the highest level of abstraction in the Verilog HDL.

Source: space-inst.blogspot.com

Source: space-inst.blogspot.com

In other words each algorithm consists of a set of instructions that execute one after the other. Behavioral models in Verilog comprise practical statements which control the replication and operate variables of the data types. They require some knowledge of how hardware or hardware signals work. Behavioral Modeling Behavioral modeling represents digital circuits at a functional and algorithmic level. The behavioral model describes a system in an algorithmic way.

Source: link.springer.com

Source: link.springer.com

Companies use behavioral modeling to target. It is primarily used to model sequential circuits but can also be used to model pure combinatorial circuits. The mechanisms statements for modeling the behavior of a design are. Furthermore the behavioral model helps in controlling the simulation and manipulate variables of the data types. EE577b Verilog for Behavioral Modeling Nestoras Tzartzanis 10 February 3 1998 Data Types.

Source: chegg.com

Source: chegg.com

Furthermore the behavioral model helps in controlling the simulation and manipulate variables of the data types. They require some knowledge of how hardware or hardware signals work. It is primarily used to model sequential circuits but can also be used to model pure combinatorial circuits. 1 Dataflow 2 Behavioral 3 Structural. Each of the technique has an action flow related with it.

Source: learnpick.in

Source: learnpick.in

Feb-9-2014 Sequential Statement Groups. Module decoder2to4 e i d. Each of the procedure has an activity flow associated with it. Verilog Style Guide Use only non-blocking assignments in always blocks Define combinational logic using assign statements whenever practical Unless if or case makes things more readable When modeling combinational logic with always blocks if a signal is assigned in one branch of an if or case it needs to be assigned. VHDL Behavioral Modeling Style.

Source: technobyte.org

Source: technobyte.org

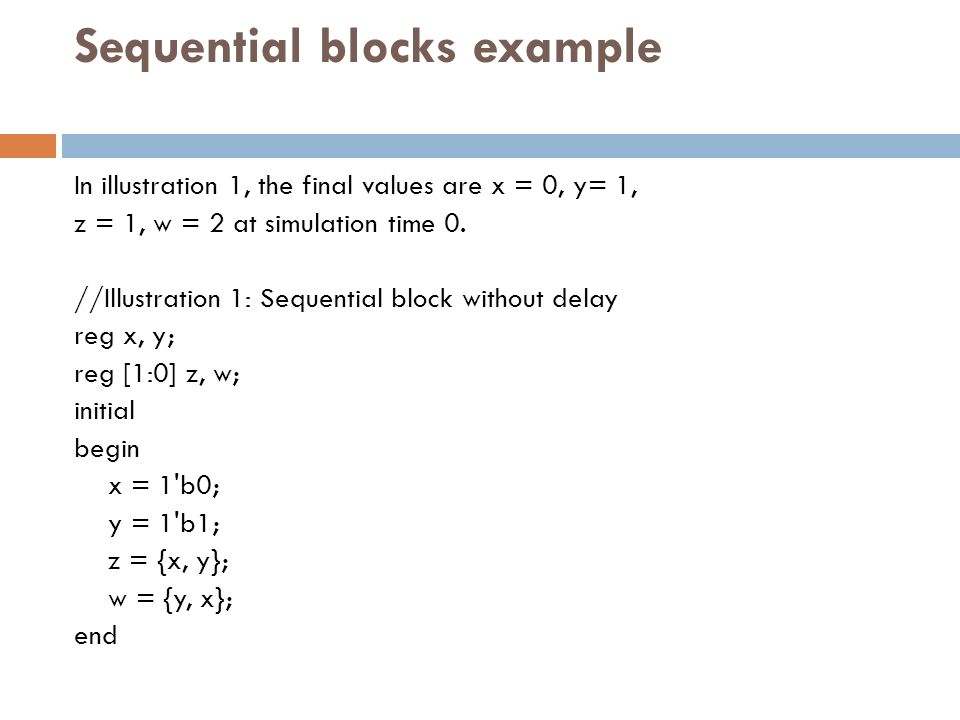

EE577b Verilog for Behavioral Modeling Nestoras Tzartzanis 10 February 3 1998 Data Types. Behavioural Modelling Timing in Verilog. It is commonly used to describe consecutive circuits but can also be used to define aggregate circuits. 1 Dataflow 2 Behavioral 3 Structural. The initial statements are executed once and the always statements are executed repetitively.

Source: slideplayer.com

Source: slideplayer.com

On the other hand The Behavioral modeling in Verilog is used to describe the function of a design in an algorithmic manner so if i want to describe a 2 to 4 decoder in dataflow modeling i would be like this. The behavioral modeling describes how the circuit should behave. The other modeling techniques are relatively detailed. This is a very powerful abstraction technique. EE577b Verilog for Behavioral Modeling Nestoras Tzartzanis 10 February 3 1998 Data Types.

This site is an open community for users to do sharing their favorite wallpapers on the internet, all images or pictures in this website are for personal wallpaper use only, it is stricly prohibited to use this wallpaper for commercial purposes, if you are the author and find this image is shared without your permission, please kindly raise a DMCA report to Us.

If you find this site beneficial, please support us by sharing this posts to your own social media accounts like Facebook, Instagram and so on or you can also save this blog page with the title what is behavioural modelling in verilog by using Ctrl + D for devices a laptop with a Windows operating system or Command + D for laptops with an Apple operating system. If you use a smartphone, you can also use the drawer menu of the browser you are using. Whether it’s a Windows, Mac, iOS or Android operating system, you will still be able to bookmark this website.