Your What is behavioral modeling in verilog images are ready in this website. What is behavioral modeling in verilog are a topic that is being searched for and liked by netizens today. You can Find and Download the What is behavioral modeling in verilog files here. Find and Download all free photos and vectors.

If you’re looking for what is behavioral modeling in verilog pictures information related to the what is behavioral modeling in verilog keyword, you have come to the ideal blog. Our site frequently provides you with suggestions for downloading the highest quality video and image content, please kindly search and locate more informative video articles and images that fit your interests.

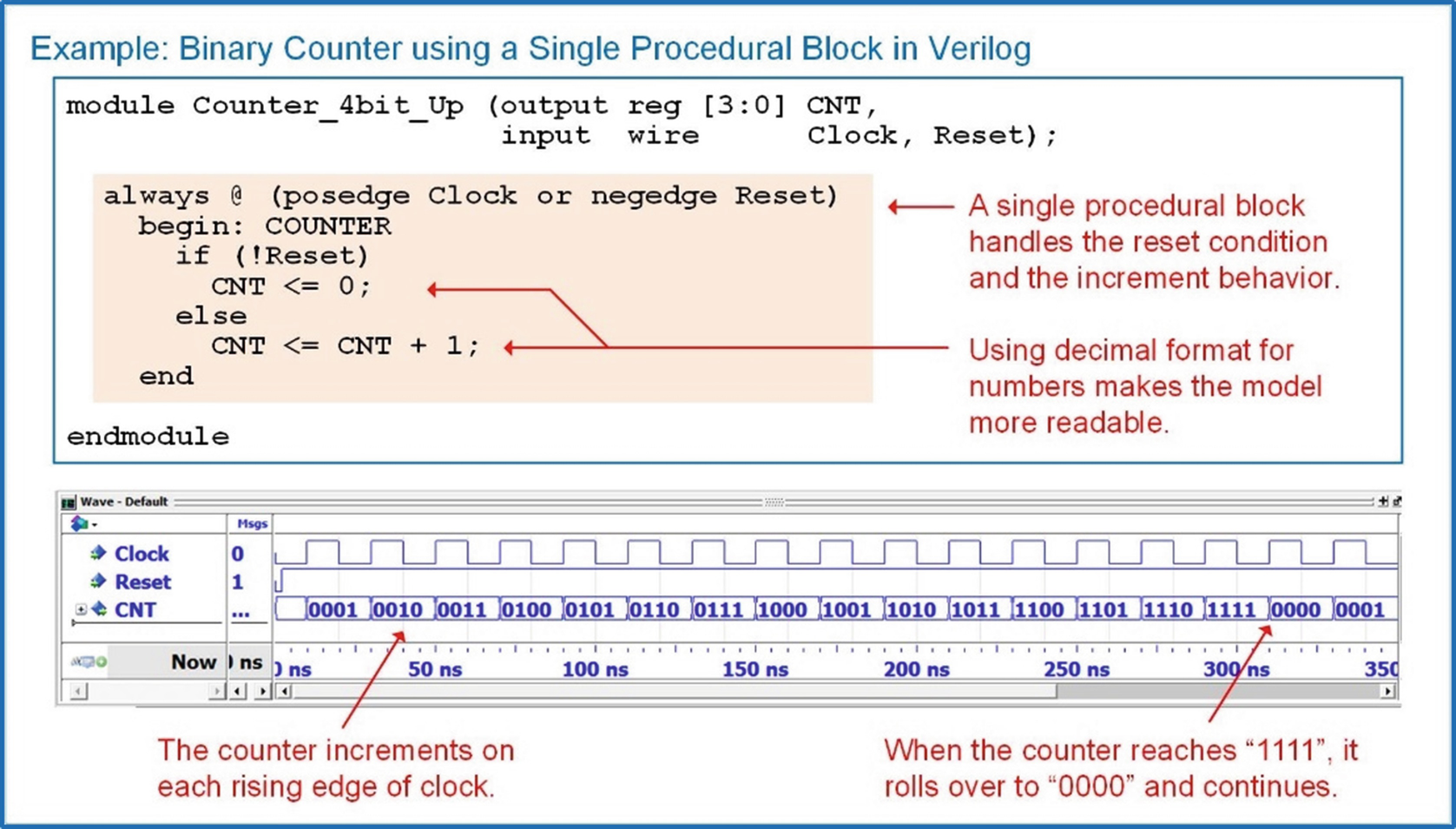

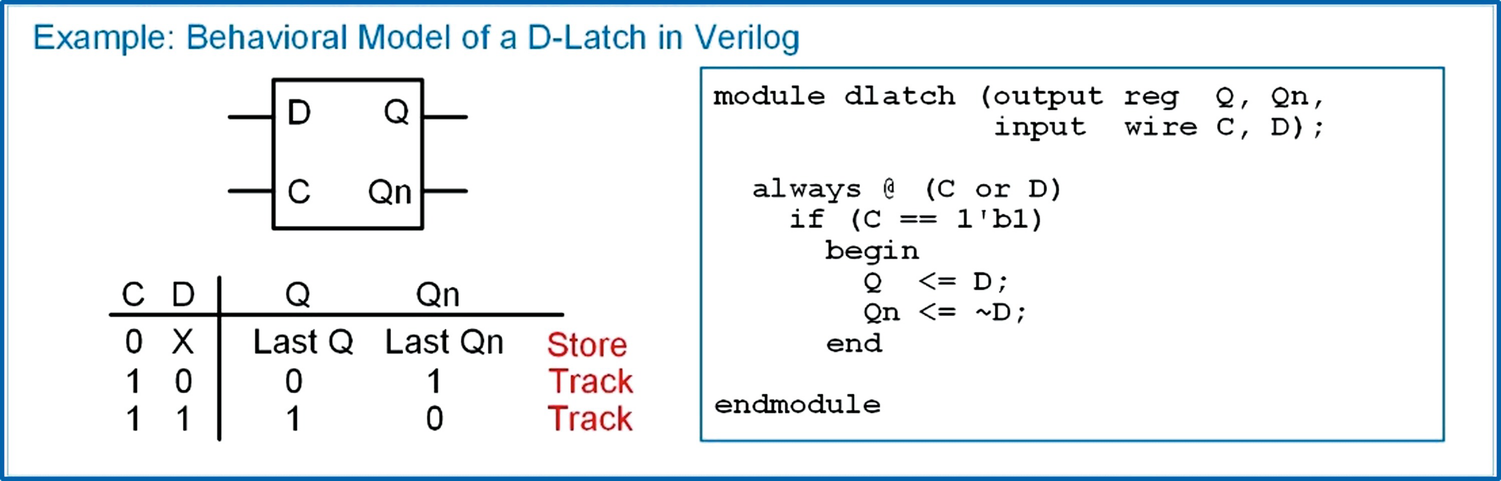

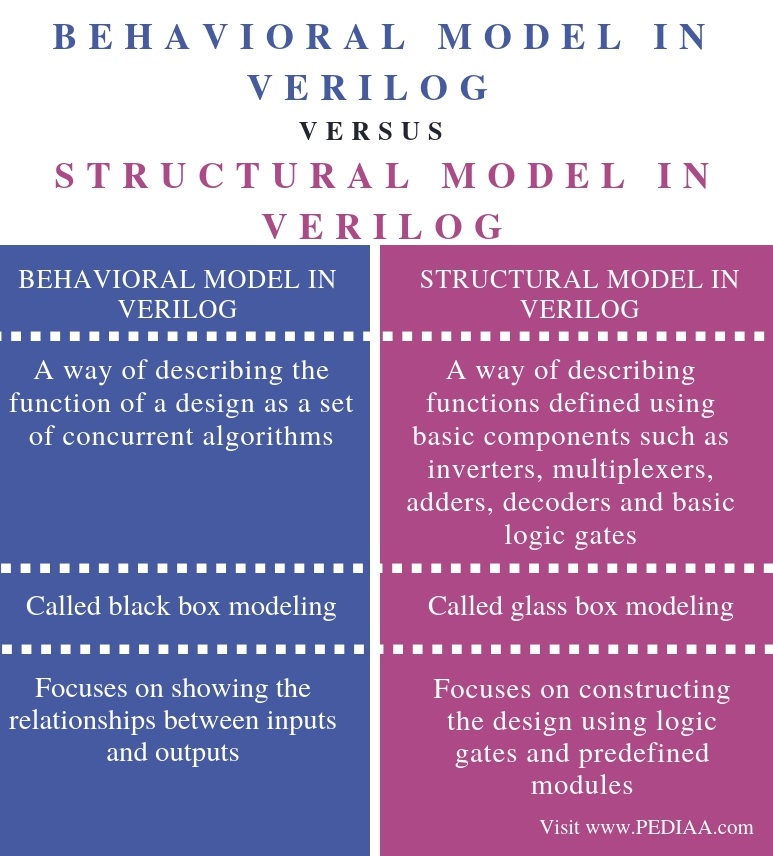

What Is Behavioral Modeling In Verilog. The functionality of a flip-flop is achieved by the connection of a certain set of gates in a particular manner. These all statements are contained within the procedures. How the gates have to be connected is usually figured out by solving K-map from the truth table. It is commonly used to describe consecutive circuits but can also be used to define aggregate circuits.

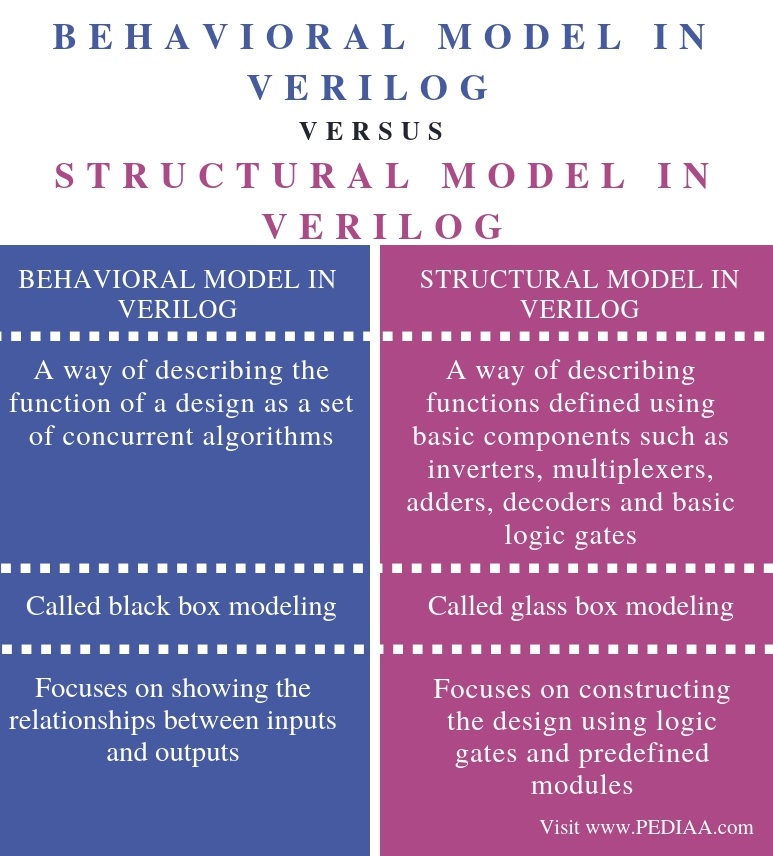

What Is The Difference Between Behavioral And Structural Model In Verilog Pediaa Com From pediaa.com

What Is The Difference Between Behavioral And Structural Model In Verilog Pediaa Com From pediaa.com

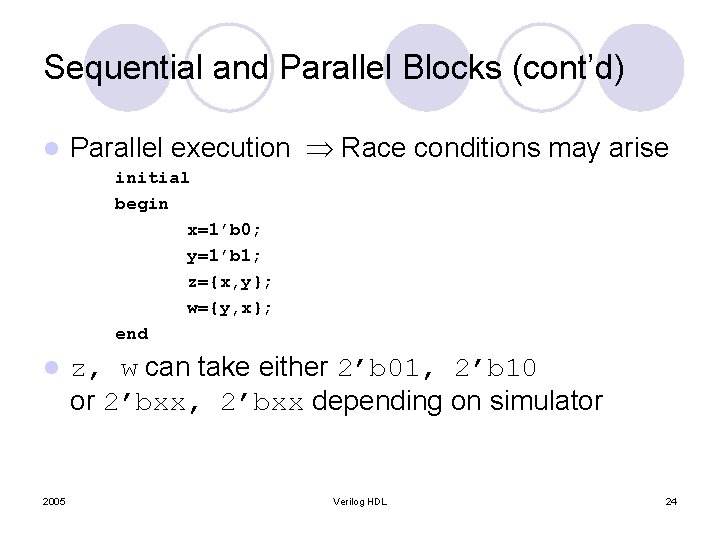

Behavioral modeling represents digital circuits at an active and prepared level. The functionality of a flip-flop is achieved by the connection of a certain set of gates in a particular manner. Group several statements together. Here each algorithm is sequential. EE577b Verilog for Behavioral Modeling Nestoras Tzartzanis 15 February 3 1998 Number Representation Constant numbers can be. Verilog HDL modeling language supports three kinds of modeling styles.

How the gates have to be connected is usually figured out by solving K-map from the truth table.

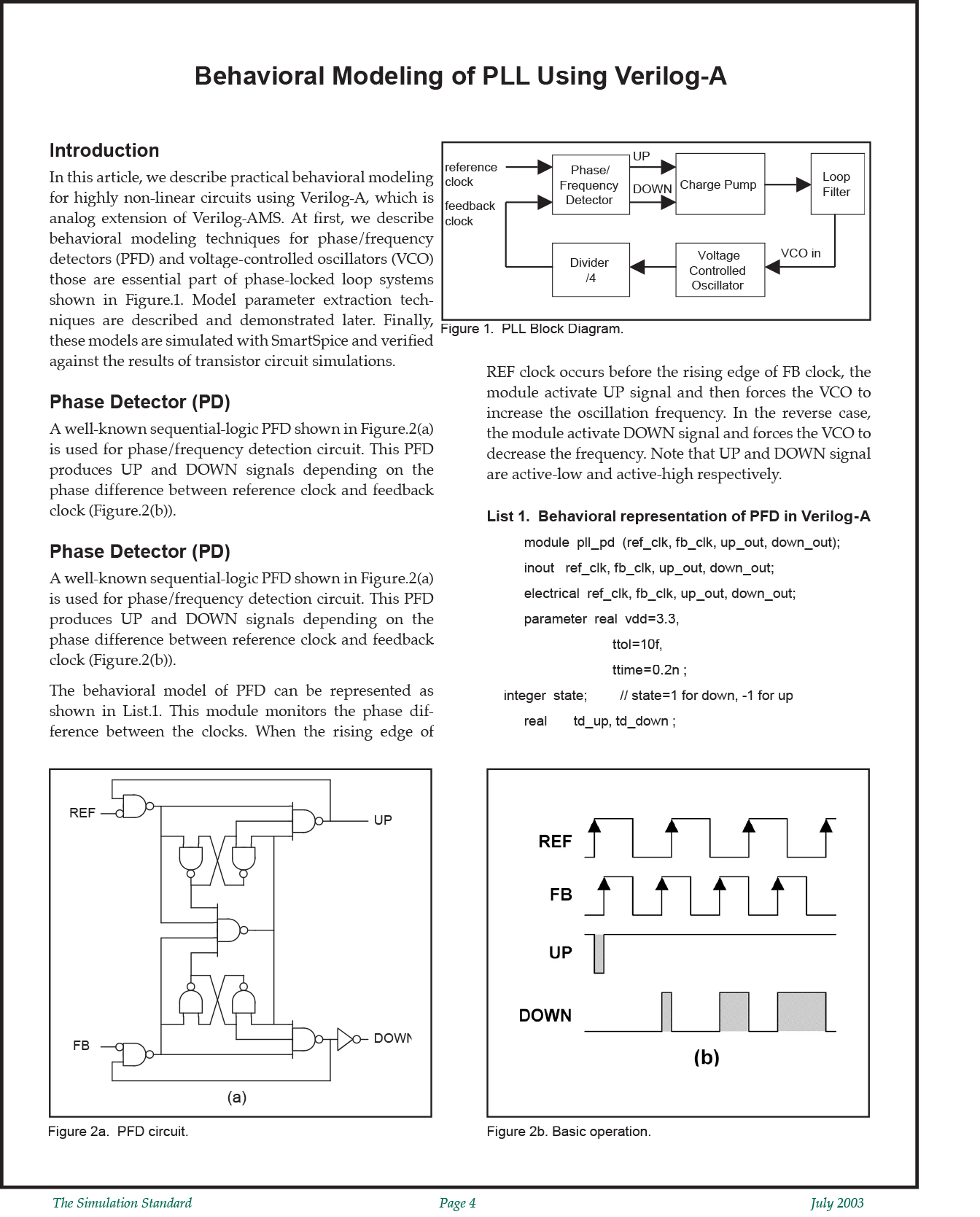

This is the highest level of abstraction provided by Verilog HDL. EE577b Verilog for Behavioral Modeling Nestoras Tzartzanis 15 February 3 1998 Number Representation Constant numbers can be. It is commonly used to describe consecutive circuits but can also be used to define aggregate circuits. In other words each algorithm consists of a set of instructions that execute one after the other. Verilog-A VerilogA is the standard behavioral modeling language in Cadence Spectre environment Allows to simulate complex systems without transistor-level implementation Some of the functionality is similar to Matlab Simulink but more circuit oriented Can interchange VerilogA Transistor-level and parasitic extracted. On the other hand The Behavioral modeling in Verilog is used to des Continue Reading Dataflow modeling in Verilog allows a digital system to be designed in terms of its function.

Source: slideplayer.com

Source: slideplayer.com

The abstraction in this modeling is as simple as writing the logic in. Behavioral models can be faster because they are not constrained eg. Verilog-A VerilogA is the standard behavioral modeling language in Cadence Spectre environment Allows to simulate complex systems without transistor-level implementation Some of the functionality is similar to Matlab Simulink but more circuit oriented Can interchange VerilogA Transistor-level and parasitic extracted. Behavioral models in Verilog contain procedural statements which control the simulation and manipulate variables of the data types. Here each algorithm is sequential.

Source: link.springer.com

Source: link.springer.com

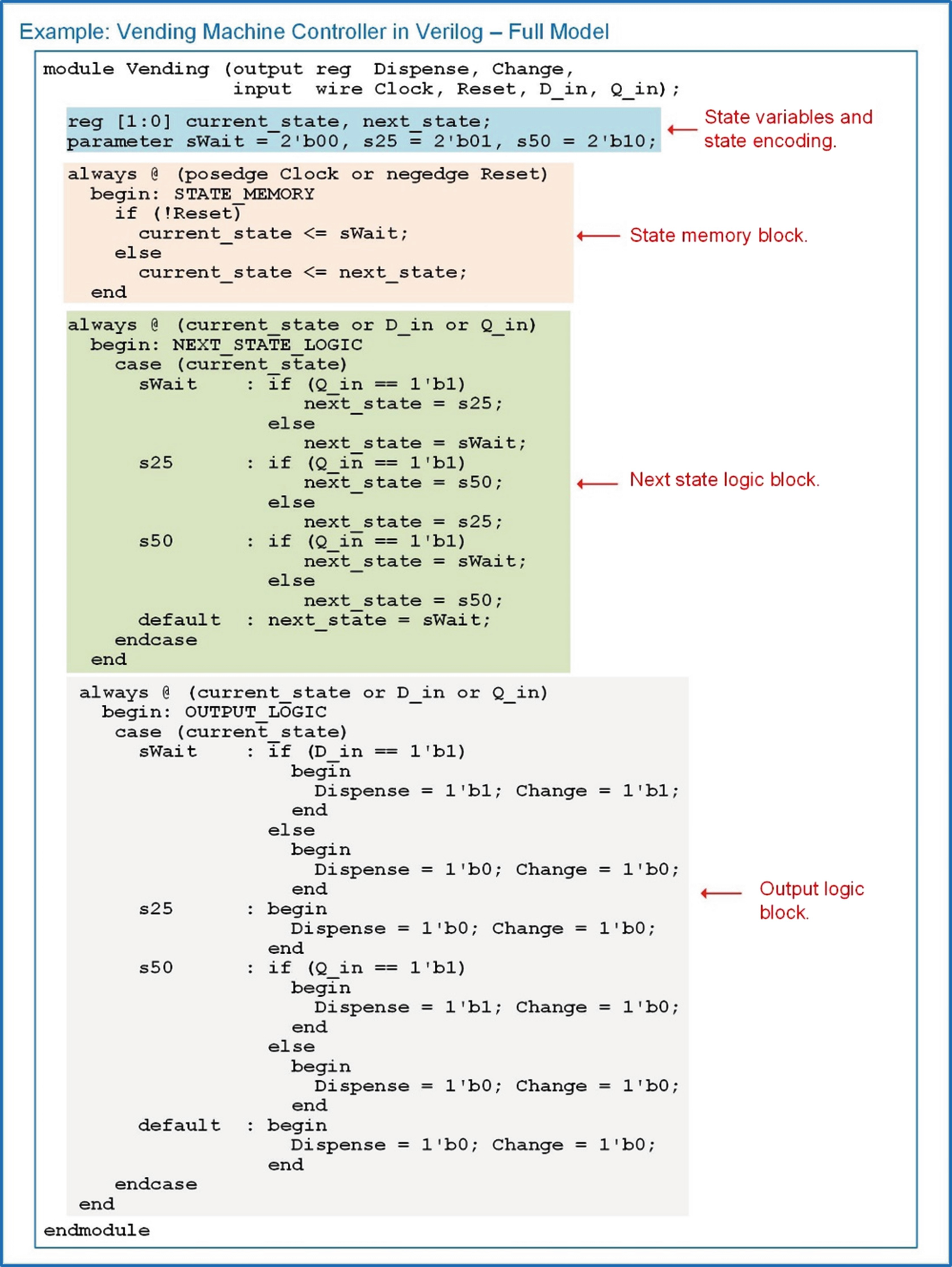

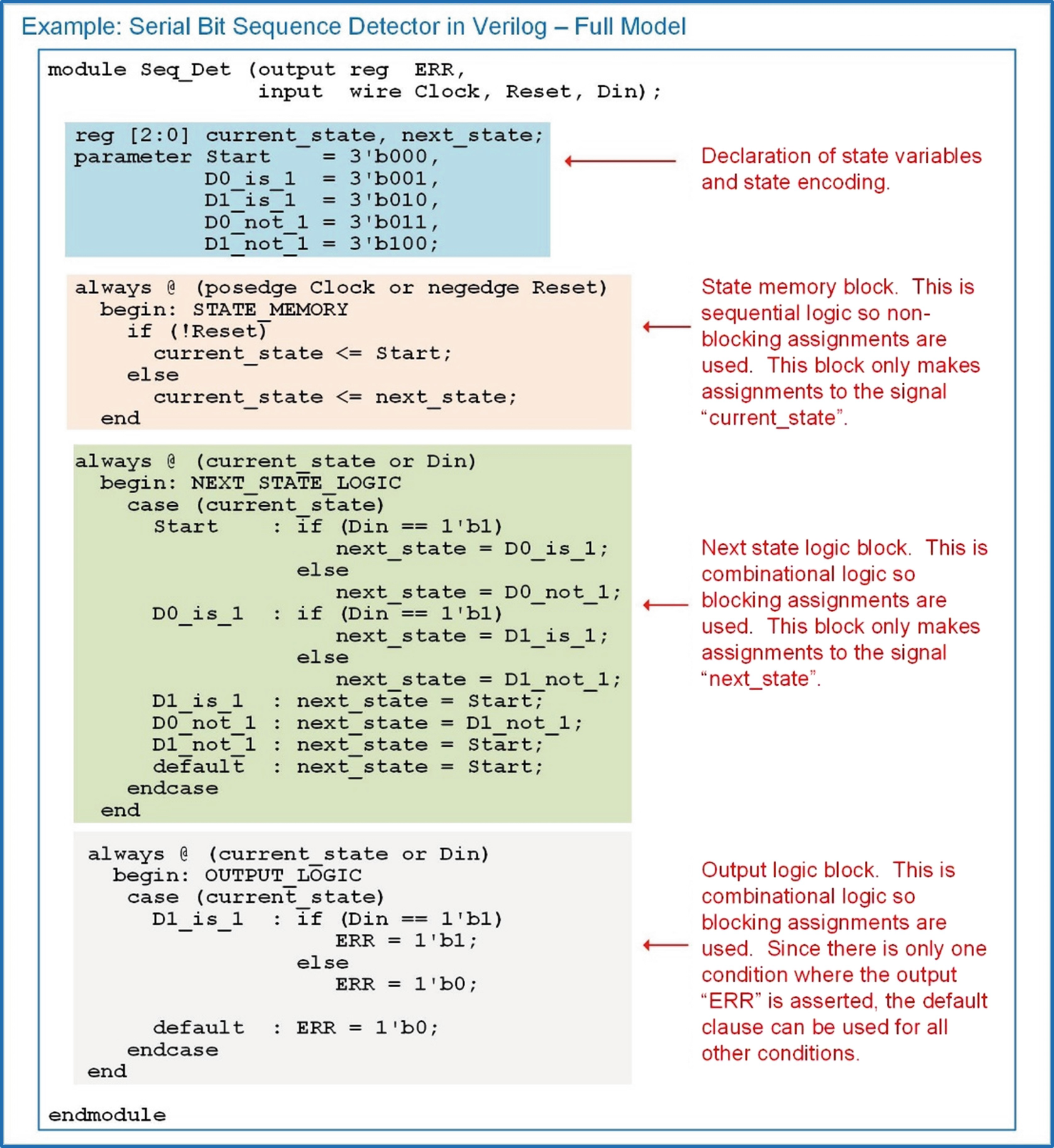

Verilog provides about 30 operator types. - It indicates how software will respond to external events or stimuli. How the gates have to be connected is usually figured out by solving K-map from the truth table. Verilog can be used at several levels automatic tools to synthesize a low-level gate-level model High-Level Behavioral Register Transfer Level Gate Level A common approach is to use CC for initial behavioral modeling and for building test rigs. More specifically its a synchronous finite state machine description.

Source: link.springer.com

Source: link.springer.com

What is Behavioural model in Verilog. The initial statements are executed once and the always statements are executed repetitively. - It indicates how software will respond to external events or stimuli. Behavioral modeling is the highest level of abstraction in the Verilog HDL. Here each algorithm is sequential.

Source: silvaco.com

Source: silvaco.com

The initial statements are executed once and the always statements are executed repetitively. Dataflow modeling describes hardware in terms of the flow of data from input to output. Here each algorithm is sequential. Furthermore the behavioral model helps in controlling the simulation and manipulate variables of the data types. The behavioral model describes a system in an algorithmic way.

Source: link.springer.com

Source: link.springer.com

The other modeling techniques are relatively detailed. Verilog-A VerilogA is the standard behavioral modeling language in Cadence Spectre environment Allows to simulate complex systems without transistor-level implementation Some of the functionality is similar to Matlab Simulink but more circuit oriented Can interchange VerilogA Transistor-level and parasitic extracted. It is commonly used to describe consecutive circuits but can also be used to define aggregate circuits. RTL is a behavioral model just within the constraints of what the synthesis tools understand. More specifically its a synchronous finite state machine description.

Source: link.springer.com

Source: link.springer.com

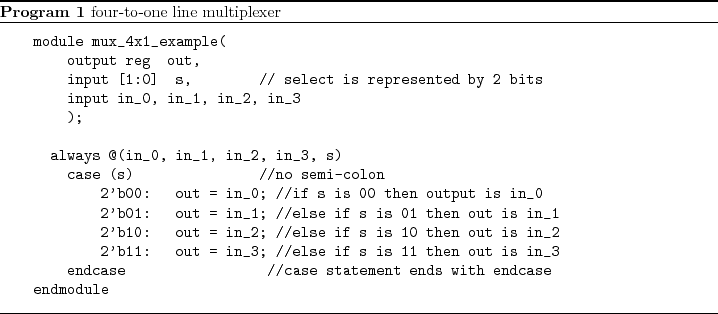

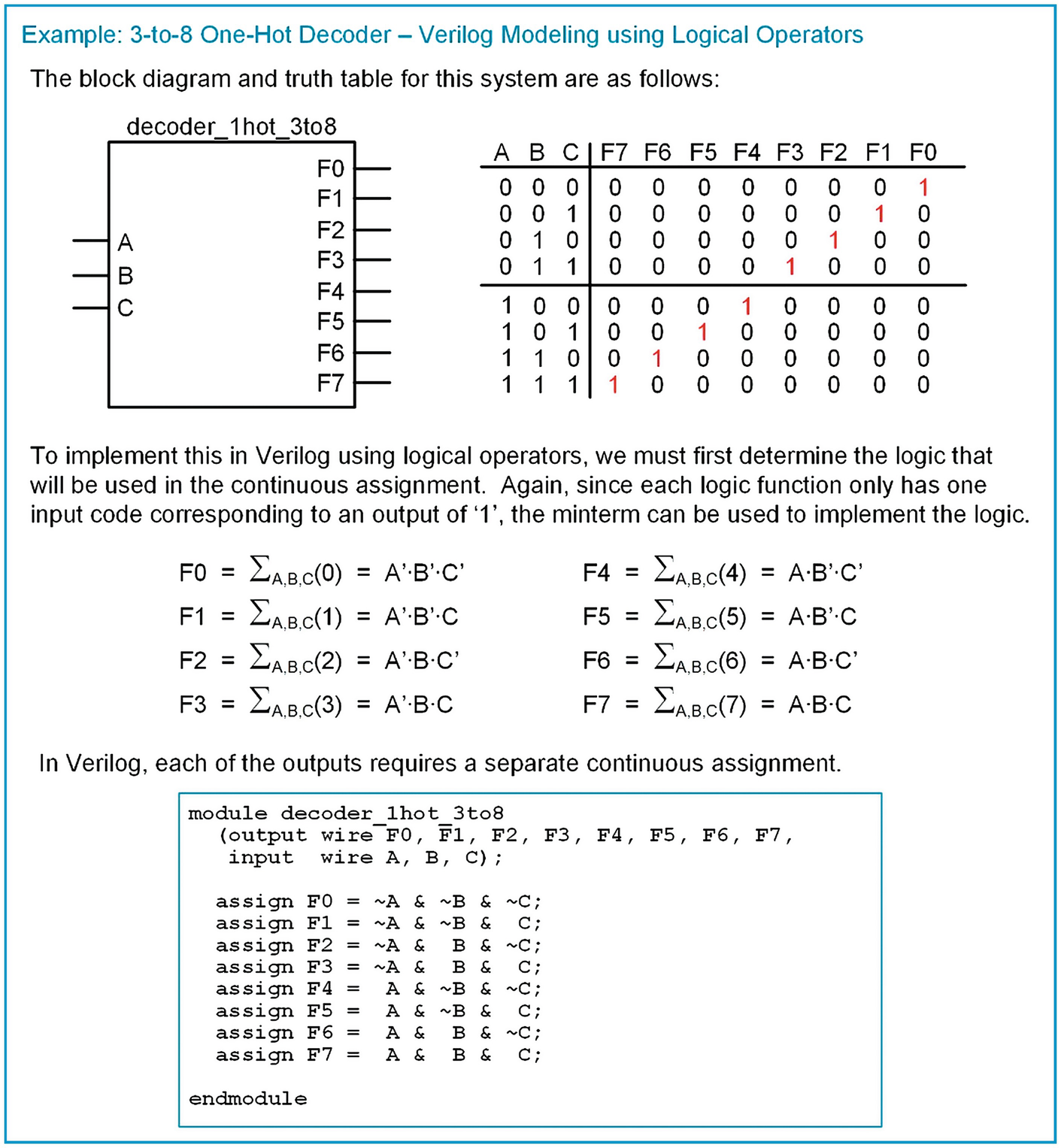

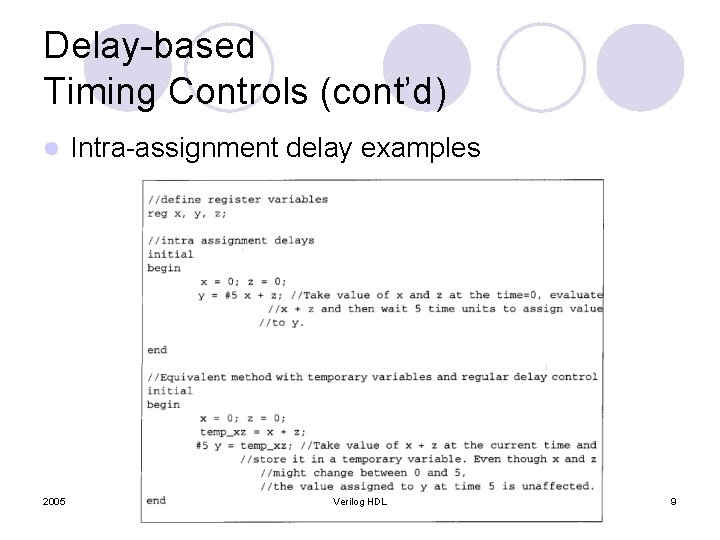

Cause the statements to be evaluated sequentially one at a time Any timing within the sequential groups is relative to the previous statement. Behavioral models in Verilog contain procedural statements which control the simulation and manipulate variables of the data types. A digital element such as a flip-flop can be represented with combinational gates like NAND and NOR. How the gates have to be connected is usually figured out by solving K-map from the truth table. The dataflow modeling style is mainly used to describe combinational circuits.

Source: learnpick.in

Source: learnpick.in

Behavioral or Algorithmic level. On the other hand The Behavioral modeling in Verilog is used to describe the function of a design in an algorithmic manner so if i want to describe a 2 to 4 decoder in dataflow modeling i would be like this. Verilog provides about 30 operator types. Cause the statements to be evaluated sequentially one at a time Any timing within the sequential groups is relative to the previous statement. The initial statements are executed once and the always statements are executed repetitively.

Source: youtube.com

Source: youtube.com

We need a way to talk about what hardware should do without. Dataflow modeling describes hardware in terms of the flow of data from input to output. Behavioral models can be faster because they are not constrained eg. A module can be implemented in terms of the desired design algorithm without concern for the hardware implementation details. A digital element such as a flip-flop can be represented with combinational gates like NAND and NOR.

Source: ee.nmt.edu

Source: ee.nmt.edu

A behavioral modelserves as an executable functional specification that documents the exact behavior of all the individual modules and their interfaces. The behavioral model describes a system in an algorithmic way. EE577b Verilog for Behavioral Modeling Nestoras Tzartzanis 15 February 3 1998 Number Representation Constant numbers can be. They require some knowledge of how hardware or hardware signals work. These all statements are contained within the procedures.

Source: pinterest.com

Source: pinterest.com

Decimal hexadecimal octal or binary Two forms of representation are available. A behavioral modelserves as an executable functional specification that documents the exact behavior of all the individual modules and their interfaces. Using asynchronous FSMs that. A module can be implemented in terms of the desired design algorithm without concern for the hardware implementation details. Behavioral models can be faster because they are not constrained eg.

Source: link.springer.com

Source: link.springer.com

They require some knowledge of how hardware or hardware signals work. On the other hand The Behavioral modeling in Verilog is used to describe the function of a design in an algorithmic manner so if i want to describe a 2 to 4 decoder in dataflow modeling i would be like this. Group several statements together. On the other hand The Behavioral modeling in Verilog is used to des Continue Reading Dataflow modeling in Verilog allows a digital system to be designed in terms of its function. Furthermore the behavioral model helps in controlling the simulation and manipulate variables of the data types.

Source: slidetodoc.com

Source: slidetodoc.com

Behavioral modeling is the highest level of abstraction in the Verilog HDL. This is the highest level of abstraction provided by Verilog HDL. Decimal hexadecimal octal or binary Two forms of representation are available. The behavioral model describes a system in an algorithmic way. The other modeling techniques are relatively detailed.

Source: docsity.com

Source: docsity.com

The functionality of a flip-flop is achieved by the connection of a certain set of gates in a particular manner. The behavioral model describes a system in an algorithmic way. Written 29 years ago by ankitpandey 900. A behavioral modelserves as an executable functional specification that documents the exact behavior of all the individual modules and their interfaces. In other words each algorithm consists of a set of instructions that execute one after the other.

Source: slideserve.com

Source: slideserve.com

Behavioral models can be faster because they are not constrained eg. RTL is a behavioral model just within the constraints of what the synthesis tools understand. Behavioral models in Verilog contain procedural statements which control the simulation and manipulate variables of the data types. They require some knowledge of how hardware or hardware signals work. Simple decimal number eg 45 507 234 etc File Size.

Source: slideplayer.com

Source: slideplayer.com

What is Behavioural model in Verilog. The other modeling techniques are relatively detailed. - It indicates how software will respond to external events or stimuli. The abstraction in this modeling is as simple as writing the logic in. Dataflow modeling uses a number of operators that act on operands to produce the desired results.

Source: slidetodoc.com

Source: slidetodoc.com

On the other hand The Behavioral modeling in Verilog is used to des Continue Reading Dataflow modeling in Verilog allows a digital system to be designed in terms of its function. Gate-level dataflow and behavioral. A behavioral modelserves as an executable functional specification that documents the exact behavior of all the individual modules and their interfaces. Decimal hexadecimal octal or binary Two forms of representation are available. They require some knowledge of how hardware or hardware signals work.

Source: pinterest.com

Source: pinterest.com

A behavioral modelserves as an executable functional specification that documents the exact behavior of all the individual modules and their interfaces. Behavioral models in Verilog contain procedural statements which control the simulation and manipulate variables of the data types. To get familiar with the dataflow and behavioral modeling of combinational circuits in Verilog HDL Background Dataflow Modeling Dataflow modeling provides the means of describing combinational circuits by their function rather than by their gate structure. Behavioral models can be faster because they are not constrained eg. Dataflow modeling uses several operators that act on operands to produce the desired results.

Source: pediaa.com

Source: pediaa.com

In other words each algorithm consists of a set of instructions that execute one after the other. In behavioral model the behavior of the system is represented as a function of specific events and time. A digital element such as a flip-flop can be represented with combinational gates like NAND and NOR. Gate-level dataflow and behavioral. Behavioral modeling represents digital circuits at an active and prepared level.

This site is an open community for users to submit their favorite wallpapers on the internet, all images or pictures in this website are for personal wallpaper use only, it is stricly prohibited to use this wallpaper for commercial purposes, if you are the author and find this image is shared without your permission, please kindly raise a DMCA report to Us.

If you find this site value, please support us by sharing this posts to your favorite social media accounts like Facebook, Instagram and so on or you can also save this blog page with the title what is behavioral modeling in verilog by using Ctrl + D for devices a laptop with a Windows operating system or Command + D for laptops with an Apple operating system. If you use a smartphone, you can also use the drawer menu of the browser you are using. Whether it’s a Windows, Mac, iOS or Android operating system, you will still be able to bookmark this website.